### INTEGRATED CIRCUITS

# DATA SHEET

# SAA5290 One page Economy Teletext/TV microcontroller

Preliminary specification

File under Integrated Circuits, IC02

February 1995

### **Philips Semiconductors**

**PHILIPS**

**SAA5290**

### **FEATURES**

### General

- Complete one page teletext decoder and TV microcontroller in a single 52-pin package

- Eastern European, Western European and Turkish language variants covered in one device

- Double size, double width and double height character capability for On-Screen Display (OSD)

- Enhanced display features including meshing and shadowing

- Separate display and acquisition timing for increased flexibility

- Minimum peripheral component count

- 525 line and 625 line display synchronization

- Standby mode through power-down of teletext and analog hardware.

#### Microcontroller

- 16 kbytes masked ROM (16 kbytes EEPROM variant for product development)

- · 256 bytes of on-chip RAM

- Six 6-bit Pulse Width Modulators (PWM) and one 14-bit precision PWM

- 4-bit Digital-to-Analog Converter (DAC) and comparator with a 3-input multiplexer allowing implementation of 3 Analog-to-Digital Converters (ADC) in software

- 2 high current (10 mA) open-drain outputs

- Interrupt logic 0 triggered on rising and falling edges, providing pulse-width measurement for remote control decoding

- Master and slave bit-level I<sup>2</sup>C-bus hardware.

### DESCRIPTION

The SAA5290 is a single-chip one page teletext decoder and television control microcontroller. The device will decode 625-line based World System Teletext transmissions and provides television control functions and On-Screen Display (OSD) functions.

The teletext decoder hardware is a derivative of the SAA5254 (IVT1.1X), and the TV control functionality provided by an on-chip industrial standard 80C51 microcontroller. A single-page static RAM is included on-board providing a complete one page teletext decoder and OSD memory.

The SAA5290 is available as a mask-programmed ROM version. An EEPROM version is also available for product development. Both versions are available in an SDIP52 package.

### ORDERING INFORMATION

| TYPE NUMBER                  | MEMORY  |        | PACKAGE                                                 |          |  |  |  |

|------------------------------|---------|--------|---------------------------------------------------------|----------|--|--|--|

| TIPE NOWIBER                 | WILWORT | NAME   | DESCRIPTION                                             | VERSION  |  |  |  |

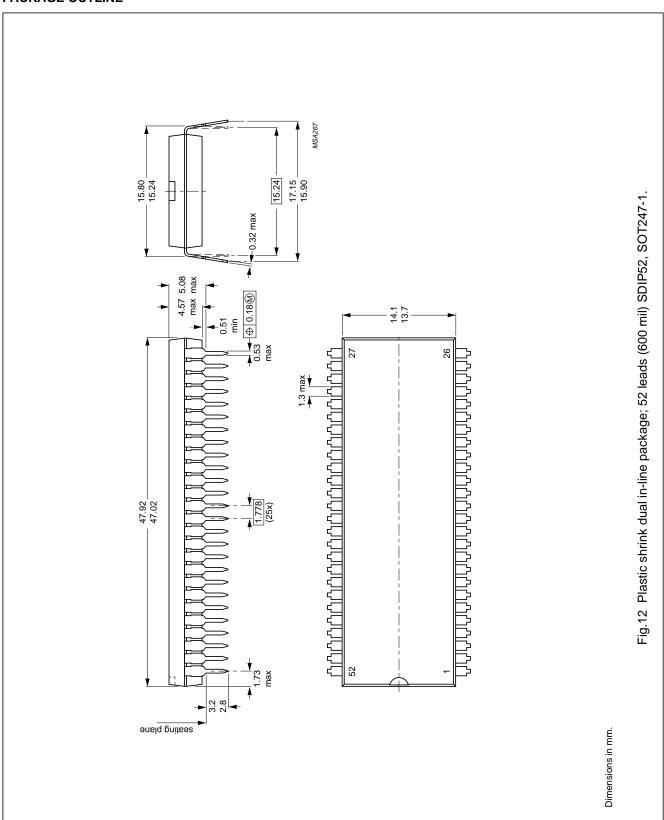

| SAA5290ZP/nnn <sup>(1)</sup> | ROM     | SDIP52 | plastic shrink dual in-line package; 52 leads (600 mil) | SOT247-1 |  |  |  |

| SAA5290ZP/NVI <sup>(2)</sup> | EEPROM  | SDIP52 | plastic shrink dual in-line package; 52 leads (600 mil) | SOT247-1 |  |  |  |

### **Notes**

- 1. nnn is a three-digit number referencing the microcontroller program ROM mask.

- 2. I is a digit number referring to the language variant of the SAA5290ZP/NV.

**SAA5290**

### **QUICK REFERENCE DATA**

| SYMBOL            | PARAMETER                      | MIN. | TYP. | MAX. | UNIT |

|-------------------|--------------------------------|------|------|------|------|

| $V_{DD}$          | supply voltage                 | 4.5  | 5.0  | 5.5  | V    |

| I <sub>DDM</sub>  | microcontroller supply current | _    | 25   | 40   | mA   |

| I <sub>DDA</sub>  | analog supply current          | _    | 35   | 50   | mA   |

| I <sub>DDT</sub>  | teletext supply current        | _    | 20   | 30   | mA   |

| f <sub>xtal</sub> | crystal frequency              | _    | 12   | _    | MHz  |

| T <sub>amb</sub>  | operating ambient temperature  | -20  | _    | +70  | °C   |

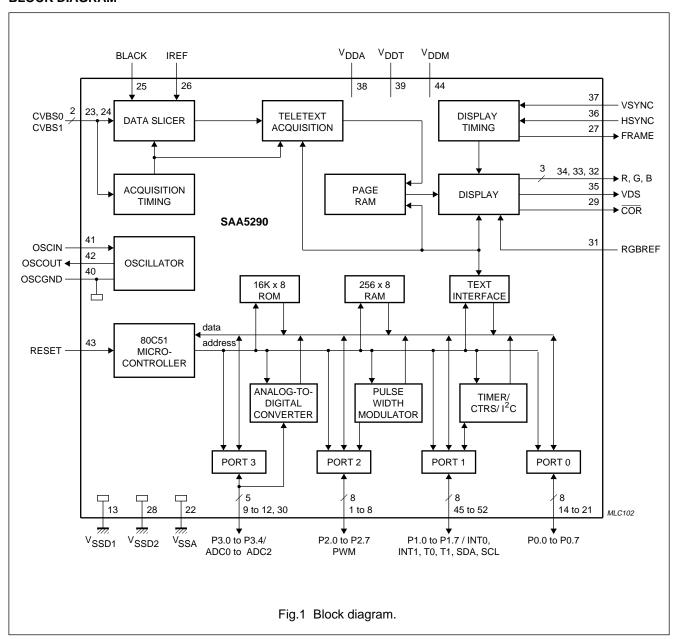

### **BLOCK DIAGRAM**

SAA5290

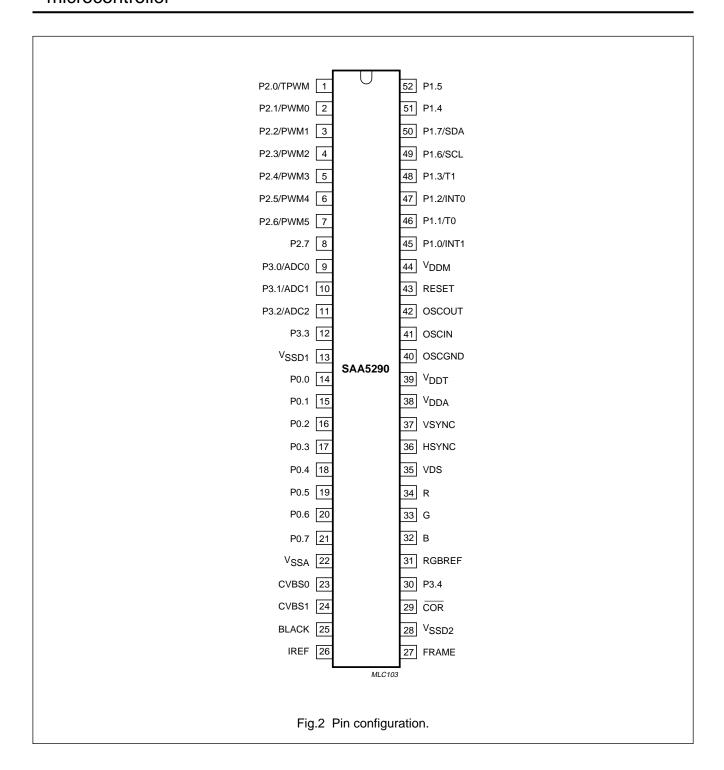

### **PINNING**

| SYMBOL            | PIN | DESCRIPTION                                                                                                                                                       |

|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2.0/TPWM         | 1   | PORT 2: 8-bit open-drain bidirectional port with alternative functions. P2.0/TPWM is the                                                                          |

| P2.1/PWM0         | 2   | output for the 14-bit high precision PWM. P2.1/PWM0 to P2.6/PWM5 are the outputs for                                                                              |

| P2.2/PWM1         | 3   | the 6-bit PWMs 0 to 5.                                                                                                                                            |

| P2.3/PWM2         | 4   |                                                                                                                                                                   |

| P2.4/PWM3         | 5   |                                                                                                                                                                   |

| P2.5/PWM4         | 6   |                                                                                                                                                                   |

| P2.6/PWM5         | 7   |                                                                                                                                                                   |

| P2.7              | 8   |                                                                                                                                                                   |

| P3.0/ADC0         | 9   | PORT 3: 5-bit open-drain bidirectional port with alternative functions. P3.0/ADC0 to                                                                              |

| P3.1/ADC1         | 10  | P3.2/ADC2 are the inputs for the software ADC facility.                                                                                                           |

| P3.2/ADC2         | 11  |                                                                                                                                                                   |

| P3.3              | 12  |                                                                                                                                                                   |

| P3.4              | 30  |                                                                                                                                                                   |

| V <sub>SSD1</sub> | 13  | digital ground 1 for teletext and microcontroller circuits.                                                                                                       |

| P0.0              | 14  | PORT 0: 8-bit open-drain bidirectional port. P0.5 and P0.6 have 10 mA current sinking                                                                             |

| P0.1              | 15  | capability at 0.5 V for direct drive of LEDs.                                                                                                                     |

| P0.2              | 16  |                                                                                                                                                                   |

| P0.3              | 17  |                                                                                                                                                                   |

| P0.4              | 18  |                                                                                                                                                                   |

| P0.5              | 19  |                                                                                                                                                                   |

| P0.6              | 20  |                                                                                                                                                                   |

| P0.7              | 21  |                                                                                                                                                                   |

| V <sub>SSA</sub>  | 22  | analog ground.                                                                                                                                                    |

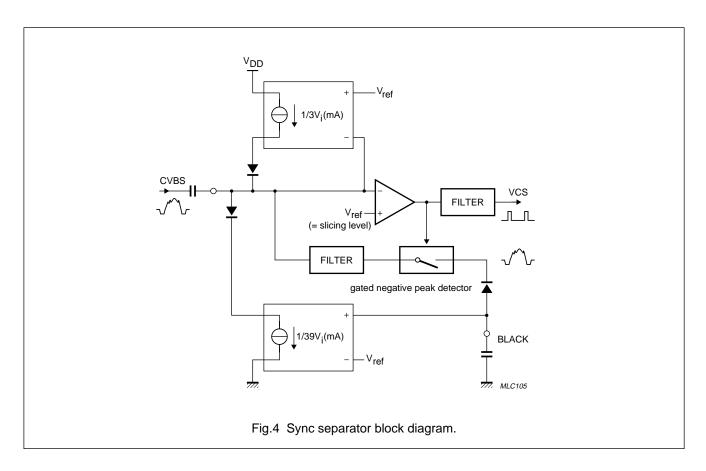

| CVBS0             | 23  | Composite video input. A positive-going 1 V (peak-to-peak) input is required, connected                                                                           |

| CVBS1             | 24  | via a 100 nF capacitor.                                                                                                                                           |

| BLACK             | 25  | Video black level storage input. This pin should be connected to V <sub>SSA</sub> via a 100 nF capacitor.                                                         |

| IREF              | 26  | Reference current input for analog circuits, connected to $V_{SSA}$ via a 27 k $\Omega$ resistor.                                                                 |

| FRAME             | 27  | De-interlace output synchronized with the VSYNC pulse to produce a non-interlaced display by adjustment of the vertical deflection currents.                      |

| V <sub>SSD2</sub> | 28  | Digital ground 2.                                                                                                                                                 |

| COR               | 29  | Open-drain, active LOW output which allows selective contrast reduction of the TV picture to enhance a mixed mode display.                                        |

| RGBREF            | 31  | DC input voltage to define the output HIGH level on the RGB pins.                                                                                                 |

| В                 | 32  | Dot rate character output of the BLUE colour information.                                                                                                         |

| G                 | 33  | Dot rate character output of the GREEN colour information.                                                                                                        |

| R                 | 34  | Dot rate character output of the RED colour information.                                                                                                          |

| VDS               | 35  | Video/data switch push-pull output for dot rate fast blanking.                                                                                                    |

| HSYNC             | 36  | Horizontal sync dedicated input for a TTL-level version of the horizontal sync pulse. The polarity of this pulse is programmable by register bit TXT1.H POLARITY. |

| SYMBOL    | PIN | DESCRIPTION                                                                                                                                                                                           |

|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSYNC     | 37  | Vertical sync dedicated input for a TTL-level version of the vertical sync pulse. The polarity of this pulse is programmable by register bit TXT1.V POLARITY.                                         |

| $V_{DDA}$ | 38  | +5 V analog power supply.                                                                                                                                                                             |

| $V_{DDT}$ | 39  | +5 V teletext power supply.                                                                                                                                                                           |

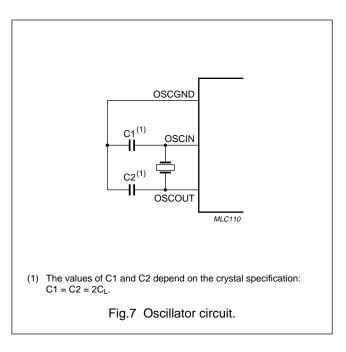

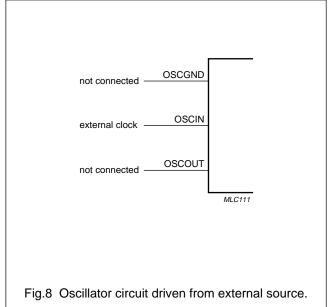

| OSCGND    | 40  | Crystal oscillator ground.                                                                                                                                                                            |

| OSCIN     | 41  | 12 MHz crystal oscillator input.                                                                                                                                                                      |

| OSCOUT    | 42  | 12 MHz crystal oscillator output.                                                                                                                                                                     |

| RESET     | 43  | If the reset input is HIGH for 2 machine cycles (24 oscillator periods) while the oscillator is running, the SAA5290 is reset. This pin should be connected to $V_{DDM}$ via a 2.2 $\mu F$ capacitor. |

| $V_{DDM}$ | 44  | +5 V microcontroller power supply.                                                                                                                                                                    |

| P1.0/INT1 | 45  | PORT 1: 8-bit open-drain bidirectional port with alternative functions. P1.0/INT1 is                                                                                                                  |

| P1.1/T0   | 46  | external interrupt 1 which can be triggered on the rising and falling edge of the pulse.                                                                                                              |

| P1.2/INT0 | 47  | P1.1/T0 is the counter/timer 0. P1.2/INT0 is external interrupt 0. P1.3/T1 is the counter/timer 1. P1.6/SCL is the serial clock input for I <sup>2</sup> C-bus. P1.7/SDA is the serial                |

| P1.3/T1   | 48  | data port for the I <sup>2</sup> C-bus.                                                                                                                                                               |

| P1.6/SCL  | 49  |                                                                                                                                                                                                       |

| P1.7/SDA  | 50  |                                                                                                                                                                                                       |

| P1.4      | 51  |                                                                                                                                                                                                       |

| P1.5      | 52  |                                                                                                                                                                                                       |

### One page Economy Teletext/TV microcontroller

**SAA5290**

### **QUALITY AND RELIABILITY**

This device will meet Philips Semiconductors General Quality Specification for Business group "Consumer Integrated Circuits SNW-FQ-611-Part E" (see "Quality Reference Handbook", order number 9398 510 63011). The principal requirements are shown in Tables 1 to 4.

### **Group A**

Table 1 Acceptance tests per lot

| TEST       | REQUIREMENTS <sup>(1)</sup> |

|------------|-----------------------------|

| Mechanical | cumulative target: <80 ppm  |

| Electrical | cumulative target: <80 ppm  |

### **Group B**

Table 2 Processability tests (by package family)

| TEST                   | REQUIREMENTS <sup>(1)</sup> |

|------------------------|-----------------------------|

| Solderability          | <7% LTPD                    |

| Mechanical             | <15% LTPD                   |

| Solder heat resistance | <15% LTPD                   |

### **Group C**

Table 3

Reliability tests (by process family)

| TEST                            | CONDITIONS                                                                       | REQUIREMENTS <sup>(1)</sup>                         |

|---------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------|

| Operational life                | 168 hours at T <sub>j</sub> = 150 °C                                             | <1500 FPM; equivalent to <100 FITS at $T_j = 70$ °C |

| Humidity life                   | temperature, humidity, bias<br>1000 hours, 85 °C, 85% RH<br>(or equivalent test) | <2000 FPM                                           |

| Temperature cycling performance | $T_{stg(min)}$ to $T_{stg(max)}$                                                 | <2000 FPM                                           |

### Table 4 Reliability tests (by device type)

| TEST             | CONDITIONS                                                | REQUIREMENTS(1) |

|------------------|-----------------------------------------------------------|-----------------|

| ESD and latch-up | ESD Human body model<br>2000 V, 100 pF, 1.5 kΩ            | <15% LTPD       |

|                  | ESD Machine model 200 V, 200 pF, 0 $\Omega$               | <15% LTPD       |

|                  | latch-up 100 mA, 1.5 × V <sub>DD</sub> (absolute maximum) | <15% LTPD       |

### Notes to Tables 1 to 4

1. ppm = fraction of defective devices, in parts per million.

LTPD = Lot Tolerance Percent Defective.

FPM = fraction of devices failing at test condition, in Failures Per Million.

FITS = Failures In Time Standard.

## One page Economy Teletext/TV microcontroller

**SAA5290**

### **LIMITING VALUES**

In accordance with Absolute Maximum Rating System (IEC 134).

| SYMBOL           | PARAMETER                                                         | CONDITIONS | MIN. | MAX.           | UNIT |

|------------------|-------------------------------------------------------------------|------------|------|----------------|------|

| V <sub>DD</sub>  | supply voltage (all supplies)                                     |            | -0.3 | +6.5           | V    |

| VI               | input voltage (any input)                                         | note 1     | -0.3 | $V_{DD} + 0.5$ | V    |

| Vo               | output voltage (any output)                                       | note 1     | -0.3 | $V_{DD} + 0.5$ | V    |

| Io               | output current (each output)                                      |            | _    | ±10            | mA   |

| I <sub>IOK</sub> | DC input or output diode current                                  |            | _    | ±20            | mA   |

| $\Delta V_{SS}$  | difference between V <sub>SSD</sub> , V <sub>SSA</sub> and OSCGND |            | _    | ±0.1           | V    |

| $\Delta V_{DD}$  | difference between $V_{DDM}$ , $V_{DDT}$ and $V_{DDA}$            | note 2     | _    | ±0.1           | V    |

| T <sub>amb</sub> | operating ambient temperature                                     |            | -20  | +70            | °C   |

| T <sub>stg</sub> | storage temperature                                               |            | -55  | +125           | °C   |

### **Notes**

- 1. This maximum value has an absolute maximum of 6.5 V independent of  $V_{\text{DD}}$ .

- 2. Except in standby mode.

### **CHARACTERISTICS**

$V_{DD}$  = 5 V  $\pm$  10%;  $V_{SS}$  = 0 V;  $T_{amb}$  = –20 to +70  $^{\circ}C$ ; unless otherwise specified.

| SYMBOL           | PARAMETER                                            | CONDITIONS            | MIN.               | TYP.                | MAX.                     | UNIT |

|------------------|------------------------------------------------------|-----------------------|--------------------|---------------------|--------------------------|------|

| Supplies         |                                                      |                       |                    | •                   |                          |      |

| V <sub>DD</sub>  | supply voltage (V <sub>DD</sub> to V <sub>SS</sub> ) |                       | 4.5                | 5.0                 | 5.5                      | V    |

| I <sub>DDM</sub> | microcontroller supply current                       |                       | _                  | 25                  | 40                       | mA   |

| I <sub>DDA</sub> | analog supply current                                |                       | _                  | 35                  | 50                       | mA   |

| I <sub>DDT</sub> | teletext supply current                              |                       | _                  | 20                  | 30                       | mA   |

| Digital inp      | uts                                                  |                       |                    |                     |                          |      |

| RESET            |                                                      |                       |                    |                     |                          |      |

| V <sub>IL</sub>  | LOW level input voltage                              |                       | -0.3               | _                   | 0.2V <sub>DD</sub> - 0.1 | V    |

| V <sub>IH</sub>  | HIGH level input voltage                             |                       | 0.7V <sub>DD</sub> | _                   | V <sub>DD</sub> + 0.3    | V    |

| ILI              | input leakage current                                | $V_I = 0$ to $V_{DD}$ | -10                | _                   | +10                      | μΑ   |

| C <sub>I</sub>   | input capacitance                                    |                       | _                  | _                   | 4                        | pF   |

| HSYNC AN         | D VSYNC                                              |                       |                    | •                   |                          | •    |

| $V_{thf}$        | switching threshold falling                          |                       | 0.2V <sub>DD</sub> | _                   | _                        | V    |

| V <sub>thr</sub> | switching threshold rising                           |                       | _                  | _                   | 0.8V <sub>DD</sub>       | V    |

| V <sub>HYS</sub> | hysteresis voltage                                   |                       | _                  | 0.33V <sub>DD</sub> | _                        | V    |

| C <sub>I</sub>   | input capacitance                                    |                       | _                  | _                   | 4                        | pF   |

# One page Economy Teletext/TV microcontroller

| SYMBOL            | PARAMETER                         | CONDITIONS                                     | MIN.                      | TYP.                | MAX.                         | UNIT |

|-------------------|-----------------------------------|------------------------------------------------|---------------------------|---------------------|------------------------------|------|

| Digital out       | tputs                             |                                                | -                         |                     | -                            | !    |

| R, G AND E        | 3 (note 1)                        |                                                |                           |                     |                              |      |

| V <sub>OL</sub>   | LOW level output voltage          | I <sub>OL</sub> = 2 mA                         | 0                         | _                   | 0.2                          | V    |

| V <sub>OH</sub>   | HIGH level output voltage         | $I_{OH} = -2 \text{ mA}$                       | V <sub>RGBREF</sub> – 0.3 | V <sub>RGBREF</sub> | V <sub>RGBREF</sub><br>+ 0.4 | V    |

| Z <sub>O</sub>    | output impedance                  |                                                | _                         | _                   | 150                          | Ω    |

| C <sub>L</sub>    | load capacitance                  |                                                | _                         | _                   | 50                           | pF   |

| Io                | DC output current                 |                                                | _                         | _                   | -4                           | mA   |

| t <sub>r</sub>    | output rise time                  | between 10% and 90%;<br>C <sub>L</sub> = 50 pF | _                         | _                   | 20                           | ns   |

| t <sub>f</sub>    | output fall time                  | between 90% and 10%;<br>C <sub>L</sub> = 50 pF | _                         | _                   | 20                           | ns   |

| COR (OPE          | N-DRAIN OUTPUT)                   | •                                              |                           | •                   | •                            | •    |

| V <sub>OH</sub>   | HIGH level pull-up output voltage |                                                | _                         | _                   | V <sub>DD</sub>              | V    |

| V <sub>OL</sub>   | LOW level output voltage          | I <sub>OL</sub> = 2 mA                         | 0                         | _                   | 0.5                          | V    |

| I <sub>OL</sub>   | LOW level output current          |                                                | _                         | _                   | 2                            | mA   |

| C <sub>L</sub>    | load capacitance                  |                                                | _                         | _                   | 25                           | pF   |

| VDS               |                                   |                                                |                           | ·                   | •                            | •    |

| V <sub>OL</sub>   | LOW level output voltage          | I <sub>OL</sub> = 1.6 mA                       | 0                         | _                   | 0.2                          | V    |

| V <sub>OH</sub>   | HIGH level output voltage         | $I_{OH} = -1.6 \text{ mA}$                     | V <sub>DD</sub> – 0.3     | _                   | $V_{DD} + 0.4$               | V    |

| C <sub>L</sub>    | load capacitance                  |                                                | _                         | _                   | 50                           | pF   |

| t <sub>r</sub>    | output rise time                  | between 10% and 90%;<br>C <sub>L</sub> = 50 pF | _                         | _                   | 20                           | ns   |

| t <sub>f</sub>    | output fall time                  | between 90% and 10%;<br>C <sub>L</sub> = 50 pF | _                         | _                   | 20                           | ns   |

| R, G, B AN        | D VDS                             | •                                              |                           |                     | •                            | •    |

| t <sub>skew</sub> | skew delay between any two pins   |                                                | _                         | _                   | 20                           | ns   |

| FRAME             | •                                 | •                                              |                           | •                   | •                            | !    |

| V <sub>OH</sub>   | HIGH level output voltage         | I <sub>OL</sub> = 8 mA                         | 0                         | _                   | 0.5                          | V    |

| V <sub>OL</sub>   | LOW level output voltage          | $I_{OL} = -8 \text{ mA}$                       | V <sub>DD</sub> – 0.5     | _                   | V <sub>DD</sub>              | V    |

| I <sub>OL</sub>   | LOW level output current          |                                                | -8                        | _                   | +8                           | mA   |

| C <sub>L</sub>    | load capacitance                  |                                                | _                         | _                   | 100                          | pF   |

# One page Economy Teletext/TV microcontroller

| V <sub>IL</sub> V <sub>IH</sub> C <sub>I</sub> V <sub>OL</sub> C <sub>L</sub> P0.5 AND P | 4, P0.7, P1.0 TO P1.5, P2.0 TO LOW level input voltage HIGH level input voltage input capacitance LOW level output voltage load capacitance | P2.7 AND P3.0 TO P3.5  I <sub>OL</sub> = 3.2 mA | -0.3<br>0.2V <sub>DD</sub> + 0.9<br>-<br>0<br>- |        | 0.2V <sub>DD</sub> - 0.1<br>V <sub>DD</sub> + 0.3<br>4<br>0.45<br>50 | V<br>V<br>pF<br>V<br>pF |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|--------|----------------------------------------------------------------------|-------------------------|

| V <sub>IL</sub> V <sub>IH</sub> C <sub>I</sub> V <sub>OL</sub> C <sub>L</sub> P0.5 AND P | LOW level input voltage HIGH level input voltage input capacitance LOW level output voltage load capacitance 0.6 LOW level input voltage    |                                                 | 0.2V <sub>DD</sub> + 0.9                        | -<br>- | V <sub>DD</sub> + 0.3<br>4<br>0.45                                   | V<br>pF<br>V            |

| V <sub>IH</sub> C <sub>I</sub> V <sub>OL</sub> C <sub>L</sub> P0.5 AND P                 | HIGH level input voltage input capacitance LOW level output voltage load capacitance 0.6 LOW level input voltage                            | I <sub>OL</sub> = 3.2 mA                        | 0.2V <sub>DD</sub> + 0.9                        | -<br>- | V <sub>DD</sub> + 0.3<br>4<br>0.45                                   | V<br>pF<br>V            |

| C <sub>I</sub> V <sub>OL</sub> C <sub>L</sub> P0.5 AND P                                 | input capacitance  LOW level output voltage load capacitance  0.6  LOW level input voltage                                                  | I <sub>OL</sub> = 3.2 mA                        | _                                               |        | 4<br>0.45                                                            | pF<br>V                 |

| V <sub>OL</sub> C <sub>L</sub> P0.5 AND P                                                | LOW level output voltage load capacitance 0.6 LOW level input voltage                                                                       | I <sub>OL</sub> = 3.2 mA                        |                                                 |        | 0.45                                                                 | V                       |

| C <sub>L</sub><br>P0.5 AND P                                                             | load capacitance 0.6 LOW level input voltage                                                                                                | I <sub>OL</sub> = 3.2 mA                        | 0 –                                             |        |                                                                      |                         |

| P0.5 AND P                                                                               | 0.6  LOW level input voltage                                                                                                                |                                                 | _                                               | _      | 50                                                                   | pF                      |

| -                                                                                        | LOW level input voltage                                                                                                                     |                                                 |                                                 |        | •                                                                    |                         |

| 1/                                                                                       |                                                                                                                                             |                                                 |                                                 |        |                                                                      |                         |

| $V_{IL}$                                                                                 | HIGH level input voltage                                                                                                                    |                                                 | -0.3                                            | _      | 0.2V <sub>DD</sub> - 0.1                                             | V                       |

| V <sub>IH</sub>                                                                          | The Thove input veltage                                                                                                                     |                                                 | 0.2V <sub>DD</sub> + 0.9                        | _      | V <sub>DD</sub> + 0.3                                                | V                       |

| Cı                                                                                       | input capacitance                                                                                                                           |                                                 | _                                               | _      | 4                                                                    | pF                      |

| V <sub>OL</sub>                                                                          | LOW level output voltage                                                                                                                    | I <sub>OL</sub> = 10 mA                         | 0                                               | _      | 0.45                                                                 | V                       |

| C <sub>L</sub>                                                                           | load capacitance                                                                                                                            |                                                 | _                                               | _      | 50                                                                   | pF                      |

| P1.6 AND P                                                                               | 1.7                                                                                                                                         |                                                 |                                                 |        | ·                                                                    |                         |

| V <sub>IL</sub>                                                                          | LOW level input voltage                                                                                                                     |                                                 | -0.3                                            | _      | +1.5                                                                 | ٧                       |

| V <sub>IH</sub>                                                                          | HIGH level input voltage                                                                                                                    |                                                 | 3.0                                             | _      | V <sub>DD</sub> + 0.3                                                | V                       |

| C <sub>I</sub>                                                                           | input capacitance                                                                                                                           |                                                 | _                                               | _      | 5                                                                    | pF                      |

| V <sub>OL</sub>                                                                          | LOW level output voltage                                                                                                                    | I <sub>OL</sub> = 3 mA                          | 0                                               | _      | 0.5                                                                  | V                       |

| C <sub>L</sub>                                                                           | load capacitance                                                                                                                            |                                                 | _                                               | _      | 400                                                                  | pF                      |

| t <sub>f</sub>                                                                           | output fall time                                                                                                                            | between 3 and 1 V                               | _                                               | _      | 200                                                                  | ns                      |

| Analog inp                                                                               | outs                                                                                                                                        |                                                 |                                                 |        |                                                                      |                         |

| CVBS0 AND                                                                                | CVBS1                                                                                                                                       |                                                 |                                                 |        |                                                                      |                         |

| V <sub>sync</sub>                                                                        | sync voltage amplitude                                                                                                                      |                                                 | 0.1                                             | 0.3    | 0.6                                                                  | V                       |

| $V_{\text{vid(p-p)}}$                                                                    | video input voltage amplitude (peak-to-peak value)                                                                                          |                                                 | 0.7                                             | 1.0    | 1.4                                                                  | V                       |

| Z <sub>source</sub>                                                                      | source impedance                                                                                                                            |                                                 | _                                               | _      | 250                                                                  | Ω                       |

| V <sub>IH</sub>                                                                          | HIGH level input voltage                                                                                                                    |                                                 | 3.0                                             | _      | V <sub>DD</sub> + 0.3                                                | V                       |

| Z <sub>I</sub>                                                                           | input impedance                                                                                                                             |                                                 | 2.5                                             | 5.0    | _                                                                    | kΩ                      |

| C <sub>I</sub>                                                                           | input capacitance                                                                                                                           |                                                 | _                                               | _      | 10                                                                   | pF                      |

| IREF                                                                                     |                                                                                                                                             |                                                 | ·                                               |        | ,                                                                    |                         |

| R <sub>gnd</sub>                                                                         | resistor to ground                                                                                                                          |                                                 | _                                               | 27     | _                                                                    | kΩ                      |

| RGBREF (r                                                                                | note 1)                                                                                                                                     |                                                 |                                                 | •      | •                                                                    |                         |

| VI                                                                                       | input voltage                                                                                                                               |                                                 | -0.3                                            | _      | V <sub>DD</sub>                                                      | V                       |

| l <sub>l</sub>                                                                           | DC input current                                                                                                                            |                                                 |                                                 | _      | 12                                                                   | mA                      |

# One page Economy Teletext/TV microcontroller

**SAA5290**

| SYMBOL                            | PARAMETER                                      | CONDITIONS               | MIN.               | TYP. | MAX.                     | UNIT |

|-----------------------------------|------------------------------------------------|--------------------------|--------------------|------|--------------------------|------|

| ADC0, AD                          | C1 AND ADC2                                    | 1                        | -                  | •    |                          | -    |

| V <sub>IL</sub>                   | LOW level input voltage                        |                          | -0.3               | _    | V <sub>DD</sub>          | V    |

| Analog in                         | put/output                                     |                          | •                  |      | •                        | •    |

| BLACK                             |                                                |                          |                    |      |                          |      |

| C <sub>black</sub>                | storage capacitor to ground                    |                          | _                  | 100  | _                        | nF   |

| V <sub>black</sub>                | black level voltage for nominal sync amplitude |                          | 1.8                | 2.15 | 2.5                      | V    |

| ILI                               | input leakage current                          |                          | -10                | _    | +10                      | μΑ   |

| Crystal os                        | cillator                                       |                          |                    |      |                          | •    |

| OSCIN                             |                                                |                          |                    |      |                          |      |

| V <sub>IL</sub>                   | LOW level input voltage                        |                          | -0.3               | _    | 0.2V <sub>DD</sub> - 0.1 | V    |

| V <sub>IH</sub>                   | HIGH level input voltage                       |                          | 0.7V <sub>DD</sub> | _    | V <sub>DD</sub> + 0.3    | V    |

| C <sub>I</sub>                    | input capacitance                              |                          | _                  | _    | 10                       | pF   |

| OSCOUT                            |                                                |                          | ·                  |      |                          |      |

| f <sub>osc</sub>                  | crystal oscillator frequency                   |                          |                    | 12   | _                        | MHz  |

| C <sub>O</sub> output capacitance |                                                |                          | _                  | _    | 10                       | pF   |

| CRYSTAL SPECIFICATION (note 2)    |                                                |                          |                    |      |                          |      |

| f <sub>xtal</sub>                 | nominal frequency                              |                          | -                  | 12   | _                        | MHz  |

| C <sub>L</sub>                    | load capacitance                               |                          | _                  | 32   | _                        | pF   |

| C1                                | series capacitance                             | T <sub>amb</sub> = 25 °C | _                  | 18.5 | _                        | fF   |

| C0                                | parallel capacitance                           | T <sub>amb</sub> = 25 °C | _                  | 4.9  | _                        | pF   |

| R <sub>r</sub>                    | resonance resistance                           | T <sub>amb</sub> = 25 °C | _                  | 35   | _                        | Ω    |

| T <sub>xtal</sub>                 | temperature range                              |                          | -20                | +25  | +70                      | °C   |

| X <sub>j</sub>                    | adjustment tolerance                           | T <sub>amb</sub> = 25 °C | _                  | _    | $\pm 50 \times 10^{-6}$  |      |

| X <sub>d</sub>                    | drift                                          |                          | _                  | _    | ±30 × 10 <sup>-6</sup>   |      |

### Notes

- 1. All RGB current is sourced from the RGBREF pin. The maximum effective series resistance between RGBREF and the R, G and B pins is 150  $\Omega$ .

- 2. Crystal order number 4322 143 05561.

### One page Economy Teletext/TV microcontroller

**SAA5290**

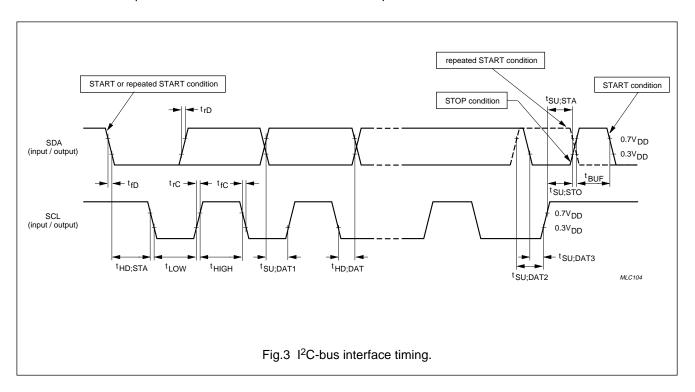

**Table 5** Characteristics for the I<sup>2</sup>C-bus interface

| SYMBOL               | PARAMETER                  | INPUT   | OUTPUT          | I <sup>2</sup> C-BUS SPECIFICATION |

|----------------------|----------------------------|---------|-----------------|------------------------------------|

| SCL timing           | g                          |         |                 |                                    |

| t <sub>HD;STA</sub>  | START condition hold time  | ≥4.0 μs | note 1          | ≥4.0 µs                            |

| t <sub>LOW</sub>     | SCL LOW time               | ≥4.7 μs | note 1          | ≥4.7 µs                            |

| t <sub>HIGH</sub>    | SCL HIGH time              | ≥4.0 μs | ≥4.0 µs; note 2 | ≥4.0 µs                            |

| t <sub>rC</sub>      | SCL rise time              | ≤1.0 μs | note 3          | ≤1.0 μs                            |

| t <sub>fC</sub>      | SCL fall time              | ≤0.3 μs | ≤0.3 μs; note 4 | ≤0.3 μs                            |

| SDA timin            | g                          |         |                 |                                    |

| t <sub>SU;DAT1</sub> | data set-up time           | ≥250 ns | note 1          | ≥250 ns                            |

| t <sub>HD;DAT</sub>  | data hold time             | ≥0 ns   | note 1          | ≥0 ns                              |

| t <sub>SU;STA</sub>  | repeated START set-up time | ≥4.7 μs | note 1          | ≥4.7 µs                            |

| t <sub>SU;STO</sub>  | STOP condition set-up time | ≥4.0 μs | note 1          | ≥4.0 µs                            |

| t <sub>BUF</sub>     | bus free time              | ≥4.7 μs | note 1          | ≥4.7 µs                            |

| t <sub>rD</sub>      | SDA rise time              | ≤1.0 μs | note 3          | ≤1.0 μs                            |

| t <sub>fD</sub>      | SDA fall time              | ≤0.3 μs | ≤0.3 μs; note 4 | ≤0.3 μs                            |

### **Notes**

- 1. This parameter is determined by the user software. It must comply with the I<sup>2</sup>C-bus specification.

- 2. This value gives the auto-clock pulse length which meets the I<sup>2</sup>C-bus specification for the special crystal frequency. Alternatively, the SCL pulse must be timed by software.

- 3. The rise time is determined by the external bus line capacitance and pull-up resistor. It must be less than 1 µs.

- 4. The maximum capacitance on bus lines SDA and SCL is 400 pF.

**SAA5290**

### **FUNCTIONAL DESCRIPTION**

### Introduction

The SAA5290 is an integrated teletext decoder and microcontroller. The teletext decoder is derived from the SAA5254 single page teletext decoder IC, with a number of enhancements to increase its suitability for on-screen display applications. The microcontroller is a derivative of the industry standard 80C51 microcontroller. A block diagram of the SAA5290 is given in Fig.1.

### Microcontroller

The functionality of the microcontroller used on the SAA5290 is described here with reference to the industry standard 80C51 microcontroller. A full description of its functionality can be found in the handbook 80C51-based 8-bit microcontrollers IC20. Using the 80C51 as a reference, the changes made for the SAA5290 fall into two categories, features not supported by the SAA5290 and features found on the SAA5290 but not supported by the 80C51.

### 80C51 features not supported by the SAA5290

INTERRUPT PRIORITY

The IP SFR is not implemented and all interrupts are treated with the same priority level. The SAA5290 retains the normal prioritization of interrupts within a level.

Table 6

Interrupts and their vector addresses

| EVENT                | PROGRAM MEMORY ADDRESS |

|----------------------|------------------------|

| Reset                | 000H                   |

| External INT0        | 003H                   |

| Timer 0              | 00BH                   |

| External INT1        | 013H                   |

| Timer 1              | 01BH                   |

| I <sup>2</sup> C-bus | 053H                   |

#### **OFF-CHIP MEMORY**

The SAA5290 does not support the use of off-chip program memory or off-chip data memory. This means that the SAA5290 does not have any of  $\overline{EA}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , ALE or  $\overline{PSEN}$  pins. The 4 MOVX instructions which move data to and from external RAM should not be used.

#### **IDLE AND POWER-DOWN MODES**

Idle and power-down modes are not supported by the SAA5290. As a consequence, the respective bits in PCON are not available.

#### **UART FUNCTION**

The 80C51 UART is not available in the SAA5290. As a consequence the SCON and SBUF SFRs are removed and the ES bit in the IE SFR is unavailable.

### Additional features for the SAA5290

The following features are provided by the SAA5290 in addition to the standard 80C51 features.

### **INTERRUPTS**

The external INT1 interrupt is modified to generate an interrupt on both the rising and falling edges of the INT1 pin, when EX1 bit is set. This facility allows for software pulse width measurement for handling of a remote control.

### BIT LEVEL I<sup>2</sup>C-BUS INTERFACE

The bit-level serial I/O supports the I<sup>2</sup>C-bus. P1.6/SCL and P1.7/SDA are the serial I/O pins. These two pins meet the I<sup>2</sup>C-bus specification concerning the input levels and output drive capability. Consequently, these pins have an open-drain output configuration. All the four following modes of the I<sup>2</sup>C-bus are supported.

- · Master transmitter

- Master receiver

- Slave transmitter

**SAA5290**

· Slave receiver.

The advantages of the bit-level I<sup>2</sup>C-bus hardware, compared with a full software I<sup>2</sup>C-bus implementation are:

- The hardware can generate the SCL pulse

- Testing a single bit (RBF or WBF respectively) is sufficient as a check for error-free transmission.

The bit-level I<sup>2</sup>C-bus hardware operates on serial bit level and performs the following functions:

- · Filtering the incoming serial data and clock signals

- · Recognizing the START condition

- Generating a serial interrupt request SI after reception of a START condition and the first falling edge of the serial clock

- Recognizing the STOP condition

- · Recognizing a serial clock pulse on the SCL line

- · Latching a serial bit on the SDA line (SDI)

- Stretching the SCL LOW period of the serial clock to suspend the transfer of the next serial data bit

- Setting Read Bit Finished (RBF) when the SCL clock pulse has finished and Write Bit Finished (WBF) if there is no arbitration loss detected (i.e. SDA = logic 0 while SDO = logic 1)

- Setting a serial clock LOW-to-HIGH detected (CLH) flag

- Setting a Bus Busy (BB) flag on a START condition and clearing this flag on a STOP condition

- Releasing the SCL line and clearing the CLH, RBF and WBF flags to resume transfer to the next serial data bit

- Generating an automatic clock if the single bit data register S1BIT is used in master mode.

The following functions must be done in software:

- Handling the I<sup>2</sup>C-bus START interrupts

- · Converting serial data to parallel data when receiving

- · Converting parallel data to serial data when transmitting

- Comparing the received slave address with its own address

- Interpreting the acknowledge information

- Guarding the I<sup>2</sup>C-bus status if RBF or WBF = logic 0.

Additionally, if acting as master:

- · Generating START and STOP conditions

- · Handling bus arbitration

- · Generating serial clock pulses if S1BIT is not used.

Three SFRs support the function of the bit-level I<sup>2</sup>C-bus hardware, they are S1INT, S1BIT and S1SCS.

### LED SUPPORT

Port pins P0.5 and P0.6 have a 10 mA current sinking capability to enable LEDs to be driven directly.

### **PWM DACs**

The SAA5290 has six 6-bit PWM DACs and one14-bit PWM DAC. These allow direct control of other parts of the television.

The low resolution 6 bit DACs are controlled by their corresponding SFR (PWM0 to PWM5) and are connected as alternative outputs of Port P2. The port bit corresponding to the PWM should be set to logic 1 for correct operation of the PWM.

Table 7 Special Function Registers PWM0 to PWM5

| D7  | D6 | D5  | D4  | D3  | D2  | D1  | D0  |

|-----|----|-----|-----|-----|-----|-----|-----|

| PWE | _  | PV5 | PV4 | PV3 | PV2 | PV1 | PV0 |

If the PWE bit for a particular port is set to logic 1, the PWM is active and controls its assigned port pin. If the PWE bit is set to logic 0 the corresponding port pin is controlled by the bit in the corresponding port register for that port.

The output of the PWM is a pulse of period 21.33  $\mu$ s with a duty cycle determined by the binary value, PV5 to PV0, multiplied by 0.33  $\mu$ s. The 14 bit PWM is controlled with SFR registers TDACL and TDACH.

Table 8 Special Function Register TDACL

| D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| TD7 | TD6 | TD5 | TD4 | TD3 | TD2 | TD1 | TD0 |

Table 9 Special Function Register TDACH

| D7  | D6 | D5   | D4   | D3   | D2   | D1  | D0  |

|-----|----|------|------|------|------|-----|-----|

| PWE | _  | TD13 | TD12 | TD11 | TD10 | TD9 | TD8 |

If the PWE bit is set to logic 1, the TPWM is active and controls Port P2.0. If the PWE bit is set to logic 0 the port pin is controlled by the bit in the corresponding port register for P2.0.

The output of the TPWM is a pulse of period 42.66  $\mu s$  with a duty cycle determined by the binary value, TD13 to TD7, multiplied by 0.33  $\mu s$ .

**SAA5290**

The 7 least significant bits, TD6 to TD0, extend the HIGH time of a proportion of the pulses by 0.33  $\mu$ s. If the LSB is set then 1 in 128 cycles is extended, if bit 1 is set then 1 in 64 cycles is extended, and so on.

### SOFTWARE ADC

Up to 3 successive approximation ADCs can be implemented in software by making use of the on-board 4-bit DAC and multiplexed voltage comparator. The software ADC uses 3 analog inputs which are multiplexed with P3.0 to P3.2.

The control of the ADC is achieved using the SAD SFR. SAD.5 and SAD.6 select one of the three inputs to pass to the comparator. The other input comes from the DAC whose input is set by SAD bits 0 to 3. The output of the comparator is SAD bit 7 and is valid by the next instruction after starting the comparison by setting SAD.ST to logic 1.

### Microcontroller interfacing

The 80C51 CPU communicates with the peripheral functions using Special Function Registers (SFRs) which are addressed as RAM locations. The registers in the teletext decoder appear as normal SFRs in the microcontroller memory map, but are written to using a serial bus. This bus is controlled by dedicated hardware which uses a simple handshake system for software synchronization. The SFR memory map is given in Table 10.

SAA5290

|                      |                                 | DIRECT |            | BITA | DDRESS, S) | /MBOL OR | ALTERNA | BIT ADDRESS, SYMBOL OR ALTERNATIVE PORT FUNCTION | UNCTION |          | RESET      |

|----------------------|---------------------------------|--------|------------|------|------------|----------|---------|--------------------------------------------------|---------|----------|------------|

| COMVO                | סבמשט                           | 900    |            |      | 6          |          |         |                                                  |         |          |            |

| S I M                | DESCR.                          | (HEX)  | MSB        |      |            |          |         |                                                  |         | LSB      | (HEX)      |

| ACC <sup>(2)</sup>   | Accumulator                     | E0H    | E7         | E6   | E5         | E4       | E3      | E2                                               | E1      | E0       | H00        |

| <b>B</b> (2)         | B register                      | FOH    | F7         | F6   | F5         | F4       | F3      | F2                                               | F1      | F0       | H00        |

| DPTR:                | Data Pointer<br>(2 bytes):      |        |            |      |            |          |         |                                                  |         |          |            |

| DPH                  | High byte                       | 83H    | ı          | ı    | ı          | ı        | 1       | 1                                                | ı       | ı        | H00        |

| DPL                  | Low byte                        | 82H    | ı          | 1    | 1          | 1        | _       | 1                                                | _       | _        | H00        |

| IE(2)(3)             | Interrupt                       | A8H    | AF         | AE   | AD         | AC       | AB      | AA                                               | A9      | A8       | H0X        |

|                      | Enable                          |        | EA         | ES1  | *          | *        | ET1     | EX1                                              | ET0     | EX0      |            |

| P0 <sup>(2)</sup>    | Port 0                          | H08    | 28         | 98   | 85         | 84       | 83      | 82                                               | 81      | 80       | FFH        |

| P1 <sup>(2)</sup>    | Port 1                          | H06    | 26         | 96   | 96         | 94       | 63      | 92                                               | 16      | 06       | FFH        |

| P2 <sup>(2)</sup>    | Port 2                          | A0H    | A7         | A6   | A5         | A4       | A3      | A2                                               | A1      | A0       | FFH        |

| P3(2)(3)             | Port 3                          | ВОН    | -          | 1    | 1          | B4       | B3      | B2                                               | B1      | B0       | XXX11111B  |

| PCON <sup>(3)</sup>  | Power<br>Control                | 87H    | *          | *    | *          | *        | GF1     | GF0                                              | *       | *        | XXXX00XXB  |

| PSW(2)               | Program                         | Н0Д    | <b>2</b> 0 | De   | DS         | D4       | D3      | D2                                               | D1      | D0       | 000000000B |

|                      | Status Word                     |        | CΥ         | AC   | F0         | RS1      | RS0     | 00                                               | *       | <u>а</u> |            |

| PWM0 <sup>(3)</sup>  | Pulse Width<br>Modulator 0      | D5H    | PWE        | *    | PV5        | PV4      | PV3     | PV2                                              | PV1     | PV0      | I          |

| PWM1(3)              | Pulse Width<br>Modulator 1      | Н9О    | PWE        | *    | PV5        | PV4      | PV3     | PV2                                              | PV1     | PV0      | I          |

| PWM2 <sup>(3)</sup>  | Pulse Width<br>Modulator 2      | р7н    | PWE        | *    | PV5        | PV4      | PV3     | PV2                                              | PV1     | PV0      | I          |

| PWM3 <sup>(3)</sup>  | Pulse Width<br>Modulator 3      | рсн    | PWE        | *    | PV5        | PV4      | PV3     | PV2                                              | PV1     | PV0      | I          |

| PWM4 <sup>(3)</sup>  | Pulse Width<br>Modulator 4      | НДД    | PWE        | *    | PV5        | PV4      | PV3     | PV2                                              | PV1     | PV0      | ı          |

| PWM5 <sup>(3)</sup>  | Pulse Width<br>Modulator 5      | DEH    | PWE        | *    | PV5        | PV4      | PV3     | PV2                                              | PV1     | PV0      | I          |

| S1BIT <sup>(3)</sup> | Serial I <sup>2</sup> C<br>data | Н6О    | SDI/       | *    | *          | *        | *       | *                                                | *       | *        | H00        |

Table 10 SAA5290 Special Function Register map (note 1)

|                         |                                      | DIRECT         |             | BITA        | BIT ADDRESS, SYMBOL OR ALTERNATIVE PORT FUNCTION | MBOL OR                | ALTERNAT                         | IVE PORT FI       | UNCTION       |               | RESET |

|-------------------------|--------------------------------------|----------------|-------------|-------------|--------------------------------------------------|------------------------|----------------------------------|-------------------|---------------|---------------|-------|

| SYMBOL                  | DESCR.                               | ADDR.<br>(HEX) | MSB         |             |                                                  |                        |                                  |                   |               | LSB           | (HEX) |

| S1INT <sup>(3)</sup>    | Serial I <sup>2</sup> C<br>interrupt | DAH            | IS          | *           | *                                                | *                      | *                                | *                 | *             | *             | ı     |

| S1SCS <sup>(2)(3)</sup> | Serial I <sup>2</sup> C              | D8H            | DF          | DE          | 00                                               | 20                     | DB                               | DA                | 60            | D8            | 1     |

|                         | control                              |                | SDI/<br>SDO | SCI/<br>SDO | CLH                                              | BB                     | RBF                              | WBF               | STR           | ENS           |       |

| SAD(2) (3)              | Software                             | E8H            | EF          | Ш           |                                                  | EC                     | EB                               | EA                | E9            | E8            | H00   |

|                         | A to D                               |                | IΗΛ         | CH1         | СНО                                              | ST                     | SAD3                             | SAD2              | SAD1          | SAD0          |       |

| SP                      | Stack Pointer                        | 81H            | 8F          | 8E          | 8D                                               | 8C                     | 8B                               | 8A                | 89            | 88            | 07H   |

| TCON <sup>(2)</sup>     | Timer/counter control                | 88H            | TF1         | TR1         | TF0                                              | TR0                    | IE1                              | 1T1               | IE0           | ІТ0           | H00   |

| ТРАСН                   | TPWM<br>High byte                    | ВЗН            | PWE         | *           | TD13                                             | TD12                   | TD11                             | TD10              | TD9           | TD8           | H00   |

| TDACL                   | TPWM<br>Low byte                     | D2H            | TD7         | TD6         | TD5                                              | TD4                    | TD3                              | TD2               | TD1           | TD0           | H00   |

| TH0                     | Timer 0<br>High byte                 | 8СН            | 1           | I           | ı                                                | ı                      | ı                                | 1                 | ı             | ı             | H00   |

| TH.                     | Timer 1<br>High byte                 | 8DН            | ı           | I           | ı                                                | ı                      | ı                                | ı                 | ı             | ı             | H00   |

| TL0                     | Timer 0<br>Low byte                  | 8АН            | 1           | I           | ı                                                | 1                      | _                                | 1                 | I             | -             | H00   |

| TL1                     | Timer 1<br>Low byte                  | 8BH            | ı           | I           | ı                                                | ı                      | ı                                | ı                 | ı             | ı             | H00   |

| ТМОД                    | Timer/counter<br>mode                | H68            | GATE        | C/Ī         | M1                                               | MO                     | GATE                             | C/Ī               | M1            | M0            | H00   |

| TXT0 <sup>(3)</sup>     | Teletext<br>register 0               | С0Н            | X24<br>POS  | *           | AUTO<br>FRAME                                    | DISABLE<br>HDR<br>ROLL | DISPLAY<br>STATUS<br>ROW<br>ONLY | DISABLE<br>FRAME  | *             | *             | Н00   |

| TXT1 <sup>(3)</sup>     | Teletext<br>register 1               | С1Н            | *           | 8-BIT       | ACQ OFF                                          | X26                    | FULL                             | FIELD<br>POLARITY | H<br>POLARITY | V<br>POLARITY | H00   |

| TXT2 <sup>(3)</sup>     | Teletext<br>register 2               | С2Н            | *           | *           | *                                                | *                      | *                                | SC2               | SC1           | sco           | H00   |

| TXT3 <sup>(3)</sup>     | Teletext<br>register 3               | СЗН            | *           | *           | *                                                | PRD4                   | PRD3                             | PRD2              | PRD1          | PRD0          | H00   |

SAA5290

|                         |                         | DIRECT         |                      | BIT A         | BIT ADDRESS, SYMBOL OR ALTERNATIVE PORT FUNCTION | MBOL OR       | ALTERNAT          | IVE PORT F       | UNCTION           |                     | RESET     |

|-------------------------|-------------------------|----------------|----------------------|---------------|--------------------------------------------------|---------------|-------------------|------------------|-------------------|---------------------|-----------|

| SYMBOL                  | DESCR.                  | ADDR.<br>(HEX) | MSB                  |               |                                                  |               |                   |                  |                   | LSB                 | (HEX)     |

| TXT4 <sup>(3)</sup>     | Teletext<br>register 4  | С4Н            | *                    | *             | EAST/<br>WEST                                    | *             | B MESH<br>ENABLE  | C MESH<br>ENABLE | TRANS<br>ENABLE   | SHADOW<br>ENABLE    | H00       |

| TXT5 <sup>(3)</sup>     | Teletext<br>register 5  | C5H            | BKGND                | BKGND         | COR OUT                                          | COR IN        | TEXT<br>OUT       | TEXT IN          | PICTURE<br>ON OUT | PICTURE<br>ON IN    | 00000011B |

| TXT6 <sup>(3)</sup>     | Teletext<br>register 6  | Сен            | BKGND                | BKGND         | COR OUT                                          | COR IN        | TEXT              | TEXT IN          | PICTURE<br>ON OUT | PICTURE<br>ON IN    | 00000011B |

| TXT7 <sup>(3)</sup>     | Teletext<br>register 7  | С7Н            | STATUS<br>ROW<br>TOP | CURSOR        | CONCEAL<br>/REVEAL                               | TOP/<br>BTM   | SNG/DBL<br>HEIGHT | BOX ON<br>24     | BOX ON<br>1-23    | BOX ON 0            | H00       |

| TXT8 <sup>(3)</sup>     | Teletext<br>register 8  | СВН            | *                    | *             | *                                                | *             | *                 | *                | *                 | CVBS0/<br>CVBS1     | H00       |

| TXT9 <sup>(3)</sup>     | Teletext<br>register 9  | Н6Э            | *                    | CLEAR<br>MEM. | A0                                               | R4            | R3                | R2               | R1                | RO                  | H00       |

| TXT10 <sup>(3)</sup>    | Teletext<br>register 10 | САН            | *                    | *             | C5                                               | C4            | ငဒ                | C2               | رح<br>د           | 00                  | H00       |

| TXT11 <sup>(3)</sup>    | Teletext<br>register 11 | СВН            | D7                   | D6            | D5                                               | D4            | D3                | D2               | D1                | 00                  | H00       |

| TXT12 <sup>(3)</sup>    | Teletext<br>register 12 | SCH            | 625/525<br>SYNC      | ROM<br>VER R4 | ROM<br>VER R3                                    | ROM<br>VER R2 | ROM<br>VER R1     | ROM<br>VER R0    | TXT ON            | VIDEO<br>QUALITY    |           |

| TXT13 <sup>(2)(3)</sup> | Teletext<br>register 13 | В8Н            | Ш *                  | » BE          | * *BD                                            | » BC          | BB *              | * BA             | 89 *              | B8<br>TXT<br>I/FACE | Н00       |

|                         |                         |                |                      |               |                                                  |               |                   |                  |                   | BUSY                |           |

Jotes

The star (\*) indicates these bits are inactive and must be written to logic 0 for future compatibility.

3. SFRs are modified or added to the 80C51 SFRs.

<sup>2.</sup> SFRs are bit addressable.

Table 11 SFR description

| REGISTER                                           | FUNCTION                                                                                   |  |  |  |

|----------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| IE - Interrupt Enable                              |                                                                                            |  |  |  |

| EA                                                 | Disable all interrupts (logic 0) or use individual enable bits (logic 1).                  |  |  |  |

| ES1                                                | I <sup>2</sup> C-bus interrupt enable (logic 1).                                           |  |  |  |

| ET1                                                | Enable Timer 1 overflow interrupt (logic 1).                                               |  |  |  |

| EX1                                                | Enable external interrupt 1 (logic 1).                                                     |  |  |  |

| ET0                                                | Enable Timer 0 overflow interrupt (logic 1).                                               |  |  |  |

| EX0                                                | Enable external interrupt 0 (logic 1).                                                     |  |  |  |

| PCON - Power Contro                                | ol .                                                                                       |  |  |  |

| GF0                                                | General purpose flag bit 0.                                                                |  |  |  |

| GF1                                                | General purpose flag bit 1.                                                                |  |  |  |

| PWM0 to PWM5 - 6-b                                 | it Pulse Width Modulator control registers                                                 |  |  |  |

| PWE                                                | Activate this 6-bit PWM and take over port pin (logic 1).                                  |  |  |  |

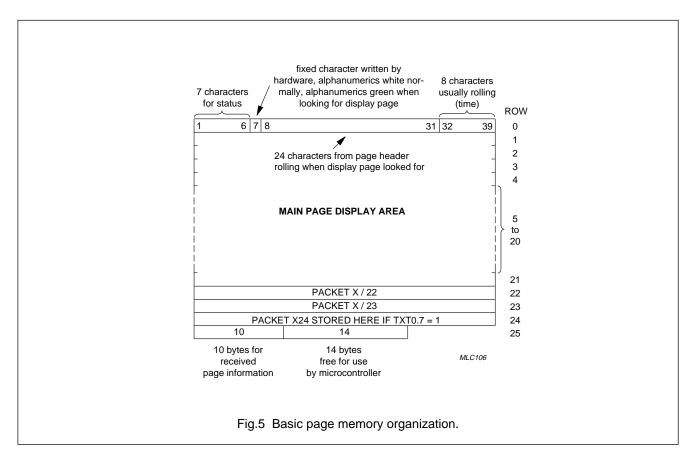

| PV0 to PV5                                         | Value to output by this 6-bit PWM.                                                         |  |  |  |